Tecnologia Científica

Novos chips 3D podem tornar a eletrônica mais rápida e mais eficiente em termos de energia

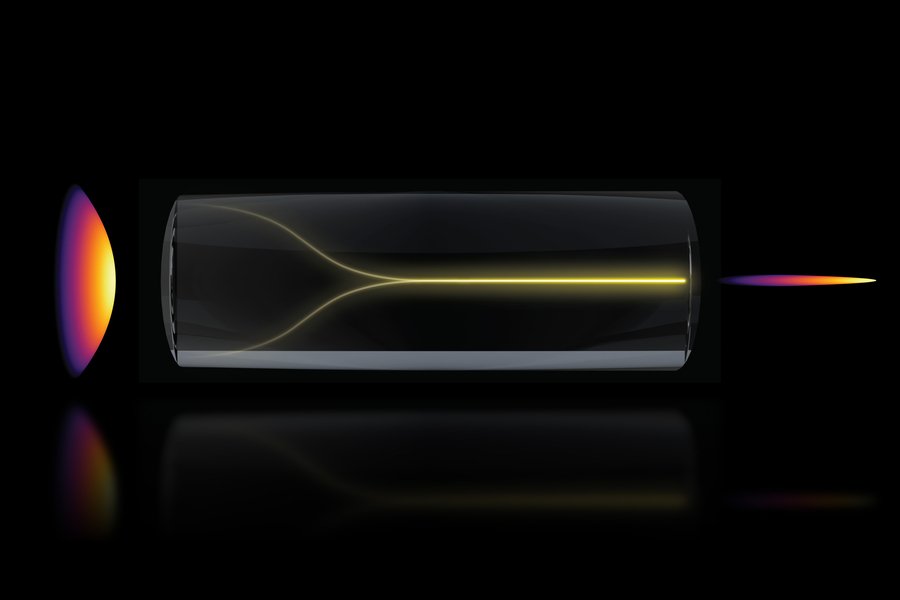

A tecnologia escalável e de baixo custo pode integrar perfeitamente transistores de nitreto de gálio de alta velocidade em um chip de silício padrão.

Pesquisadores desenvolveram um novo processo de fabricação que integra transistores de nitreto de gálio de alto desempenho em chips CMOS de silício padrão de uma forma de baixo custo e escalável. Créditos: Imagem: Cortesia dos pesquisadores

O material semicondutor avançado nitreto de gálio provavelmente será essencial para a próxima geração de sistemas de comunicação de alta velocidade e a eletrônica de potência necessária para data centers de última geração.

Infelizmente, o alto custo do nitreto de gálio (GaN) e a especialização necessária para incorporar esse material semicondutor em eletrônicos convencionais limitaram seu uso em aplicações comerciais.

Agora, pesquisadores do MIT e de outros lugares desenvolveram um novo processo de fabricação que integra transistores GaN de alto desempenho em chips CMOS de silício padrão de uma forma que é de baixo custo, escalável e compatível com as fundições de semicondutores existentes.

O método envolve construir muitos transistores minúsculos na superfície de um chip de GaN, cortar cada transistor individualmente e, então, colar apenas o número necessário de transistores em um chip de silício usando um processo de baixa temperatura que preserva a funcionalidade de ambos os materiais.

O custo permanece mínimo, visto que apenas uma pequena quantidade de material GaN é adicionada ao chip, mas o dispositivo resultante pode receber um aumento significativo de desempenho com transistores compactos e de alta velocidade. Além disso, ao separar o circuito GaN em transistores discretos que podem ser distribuídos pelo chip de silício, a nova tecnologia é capaz de reduzir a temperatura de todo o sistema.

Os pesquisadores usaram esse processo para fabricar um amplificador de potência, um componente essencial em celulares, que alcança maior intensidade de sinal e eficiência do que dispositivos com transistores de silício. Em um smartphone, isso poderia melhorar a qualidade das chamadas, aumentar a largura de banda sem fio, aprimorar a conectividade e prolongar a vida útil da bateria.

Como seu método se encaixa em procedimentos padrão, ele pode aprimorar a eletrônica existente hoje, bem como tecnologias futuras. No futuro, o novo esquema de integração pode até mesmo permitir aplicações quânticas, já que o GaN tem desempenho superior ao do silício nas temperaturas criogênicas essenciais para muitos tipos de computação quântica.

“Se pudermos reduzir o custo, melhorar a escalabilidade e, ao mesmo tempo, aprimorar o desempenho do dispositivo eletrônico, é óbvio que devemos adotar essa tecnologia. Combinamos o melhor do que existe em silício com a melhor eletrônica de nitreto de gálio possível. Esses chips híbridos podem revolucionar muitos mercados comerciais”, afirma Pradyot Yadav, aluno de pós-graduação do MIT e autor principal de um artigo sobre esse método.

Ele é acompanhado no artigo pelos colegas de pós-graduação do MIT Jinchen Wang e Patrick Darmawi-Iskandar; pelo pós-doutorado do MIT John Niroula; pelos autores seniores Ulrich L. Rohde, cientista visitante dos Laboratórios de Tecnologia de Microsistemas (MTL), e Ruonan Han, professor associado do Departamento de Engenharia Elétrica e Ciência da Computação (EECS) e membro do MTL; e Tomás Palacios, Professor Clarence J. LeBel do EECS e diretor do MTL; além de colaboradores do Georgia Tech e do Laboratório de Pesquisa da Força Aérea. A pesquisa foi recentemente apresentada no Simpósio de Circuitos Integrados de Radiofrequência do IEEE.

Troca de transistores

O nitreto de gálio é o segundo semicondutor mais utilizado no mundo, logo depois do silício, e suas propriedades únicas o tornam ideal para aplicações como iluminação, sistemas de radar e eletrônica de potência.

O material existe há décadas e, para atingir seu desempenho máximo, é importante que chips feitos de GaN sejam conectados a chips digitais feitos de silício, também chamados de chips CMOS. Para isso, alguns métodos de integração unem transistores de GaN a um chip CMOS por meio da soldagem das conexões, mas isso limita o tamanho dos transistores de GaN. Quanto menores os transistores, maior a frequência em que podem operar.

Outros métodos integram uma pastilha inteira de nitreto de gálio sobre uma pastilha de silício, mas usar tanto material é extremamente caro, especialmente porque o GaN é necessário apenas em alguns transistores minúsculos. O restante do material na pastilha de GaN é desperdiçado.

"Queríamos combinar a funcionalidade do GaN com o poder dos chips digitais feitos de silício, mas sem comprometer o custo da largura de banda. Conseguimos isso adicionando transistores discretos de nitreto de gálio superminúsculos diretamente sobre o chip de silício", explica Yadav.

Os novos chips são o resultado de um processo de várias etapas.

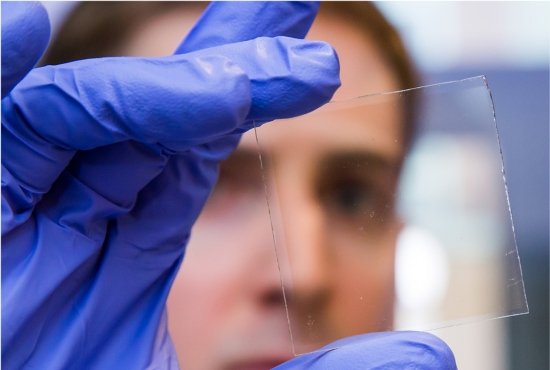

Primeiro, um conjunto compacto de transistores minúsculos é fabricado em toda a superfície de um wafer de GaN. Usando tecnologia de laser de alta precisão, eles cortam cada um deles até o tamanho exato do transistor, que é de 240 por 410 mícrons, formando o que eles chamam de dielete. (Um mícron é um milionésimo de metro.)

Cada transistor é fabricado com minúsculos pilares de cobre na parte superior, que são usados para se ligar diretamente aos pilares de cobre na superfície de um chip CMOS de silício padrão. A ligação cobre-cobre pode ser feita em temperaturas abaixo de 400 graus Celsius, o que é baixo o suficiente para evitar danos a qualquer um dos materiais.

As técnicas atuais de integração de GaN exigem ligações que utilizam ouro, um material caro que requer temperaturas muito mais altas e forças de ligação mais fortes do que o cobre. Como o ouro pode contaminar as ferramentas usadas na maioria das fundições de semicondutores, normalmente requer instalações especializadas.

"Queríamos um processo de baixo custo, baixa temperatura e baixa força, e o cobre supera todos os outros relacionados ao ouro. Ao mesmo tempo, tem melhor condutividade", diz Yadav.

Uma nova ferramenta

Para viabilizar o processo de integração, eles criaram uma nova ferramenta especializada que consegue integrar cuidadosamente o minúsculo transistor de GaN aos chips de silício. A ferramenta utiliza vácuo para segurar o dielet enquanto ele se move sobre um chip de silício, focando na interface de ligação de cobre com precisão nanométrica.

Eles usaram microscopia avançada para monitorar a interface e, então, quando o dielet estava na posição correta, eles aplicaram calor e pressão para ligar o transistor GaN ao chip.

"Para cada etapa do processo, tive que encontrar um novo colaborador que soubesse aplicar a técnica que eu precisava, aprender com ele e, então, integrar isso à minha plataforma. Foram dois anos de aprendizado constante", diz Yadav.

Depois que os pesquisadores aperfeiçoaram o processo de fabricação, eles o demonstraram desenvolvendo amplificadores de potência, que são circuitos de radiofrequência que amplificam sinais sem fio.

Seus dispositivos alcançaram maior largura de banda e melhor ganho do que os dispositivos feitos com transistores de silício tradicionais. Cada chip compacto tem uma área de menos de meio milímetro quadrado.

Além disso, como o chip de silício utilizado na demonstração é baseado na metalização de última geração e nas opções passivas do Intel FinFET 16 de 22 nm, eles conseguiram incorporar componentes frequentemente usados em circuitos de silício, como capacitores de neutralização. Isso melhorou significativamente o ganho do amplificador, aproximando-o um passo mais da próxima geração de tecnologias sem fio.

“Para lidar com a desaceleração da Lei de Moore no escalonamento de transistores, a integração heterogênea surgiu como uma solução promissora para o escalonamento contínuo do sistema, redução do fator de forma, melhoria da eficiência energética e otimização de custos. Particularmente na tecnologia sem fio, a forte integração de semicondutores compostos com wafers à base de silício é fundamental para a concretização de sistemas unificados de circuitos integrados front-end, processadores de banda base, aceleradores e memória para plataformas de antenas para IA de próxima geração. Este trabalho representa um avanço significativo ao demonstrar a integração 3D de múltiplos chips GaN com CMOS de silício e expande os limites das capacidades tecnológicas atuais”, afirma Atom Watanabe, pesquisador científico da IBM que não participou deste artigo.

Este trabalho é parcialmente financiado pelo Departamento de Defesa dos EUA, por meio do Programa de Bolsas de Pós-Graduação em Ciência e Engenharia de Defesa Nacional (NDSEG) e pelo CHIMES, um dos sete centros do JUMP 2.0, um programa da Corporação de Pesquisa em Semicondutores do Departamento de Defesa e da Agência de Projetos de Pesquisa Avançada de Defesa (DARPA). A fabricação foi realizada nas instalações do MIT Nano, do Laboratório de Pesquisa da Força Aérea e da Georgia Tech.