Tecnologia Científica

Pesquisadores revelam chip 3D inovador para acelerar a IA

Uma equipe colaborativa conseguiu produzir o primeiro chip monolítico 3D fabricado em uma fundição nos EUA, oferecendo a fiação de chip 3D mais densa e ganhos de velocidade de várias ordens de magnitude.

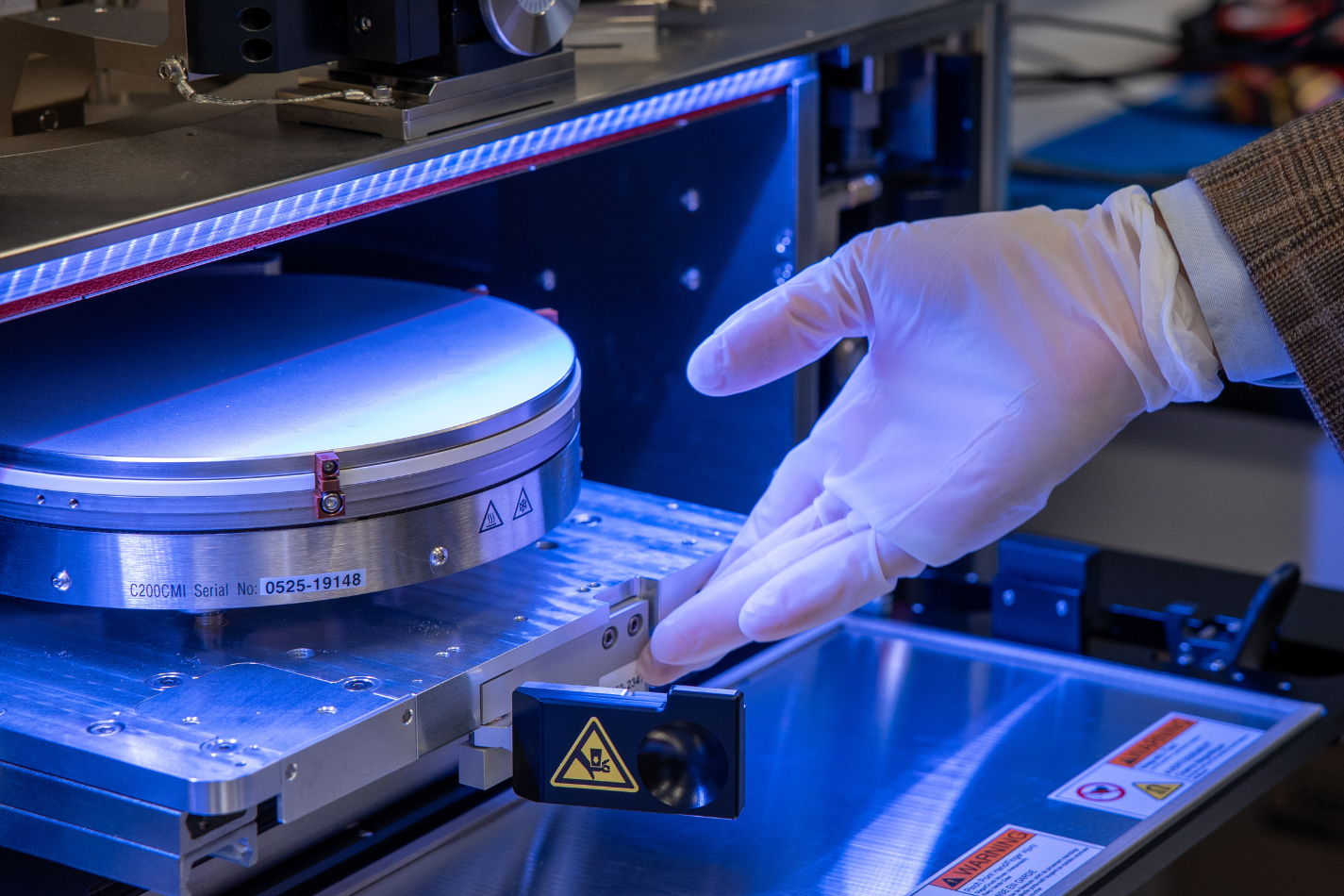

Para testar os novos chips, os pesquisadores usaram uma máquina especial, como a da imagem, para realizar a caracterização elétrica automatizada dos projetos em uma pastilha de chips. | Cortesia de Bella Ciervo, Penn Engineering

Engenheiros da Universidade de Stanford, da Universidade Carnegie Mellon, da Universidade da Pensilvânia e do Instituto de Tecnologia de Massachusetts (MIT) colaboraram com a SkyWater Technology, a maior fundição de semicondutores exclusivamente sediada nos EUA, para desenvolver um novo chip de computador multicamadas cuja arquitetura poderá inaugurar uma nova era de hardware de IA e inovação em semicondutores no país.

Ao contrário dos chips 2D, em sua maioria planos, atuais, os principais componentes ultrafinos do novo protótipo se elevam como andares em um prédio alto, com a fiação vertical funcionando como inúmeros elevadores de alta velocidade que permitem a movimentação rápida e massiva de dados. Sua densidade recorde de conexões verticais e a combinação cuidadosamente integrada de unidades de memória e computação ajudam o chip a superar os gargalos que há muito tempo dificultam o aprimoramento dos designs planos. Em testes de hardware e simulações, o novo chip 3D supera os chips 2D em aproximadamente uma ordem de magnitude.

Embora laboratórios acadêmicos já tenham construído chips 3D experimentais, esta é a primeira vez que um chip desse tipo demonstra ganhos de desempenho claros e é fabricado em uma fundição comercial. "Isso abre as portas para uma nova era de produção e inovação de chips", disse Subhasish Mitra , professor titular da Cátedra William E. Ayer de Engenharia Elétrica e professor de Ciência da Computação na Universidade Stanford, e investigador principal de um novo artigo que descreve o chip, apresentado na 71ª Reunião Anual Internacional de Dispositivos Eletrônicos (IEDM) do IEEE. "Avanços como este são o caminho para alcançarmos as melhorias de desempenho de hardware mil vezes maiores que os futuros sistemas de IA exigirão."

Os desafios para os chips planos

Os modelos modernos de IA, como o ChatGPT e o Claude, precisam transferir quantidades impressionantes de dados entre a memória, que armazena as informações, e as unidades de computação que as processam.

Em chips 2D convencionais, os componentes ficam dispostos em uma única superfície plana com memória limitada e dispersa, de modo que os dados precisam percorrer alguns caminhos longos e congestionados. Como os elementos de computação operam muito mais rápido do que os dados conseguem se mover — e como o chip não consegue armazenar memória suficiente nas proximidades — o sistema acaba constantemente aguardando informações. Os engenheiros chamam esse gargalo de "barreira de memória", o ponto em que a velocidade de processamento supera a capacidade do chip de fornecer dados.

Durante décadas, os fabricantes de chips contornaram o problema do gargalo da memória miniaturizando os transistores — os minúsculos interruptores em um chip que realizam cálculos e armazenam dados — e colocando mais deles em cada chip. Mas essa estratégia também está se aproximando de limites físicos intransponíveis, que os pesquisadores chamam de "barreira da miniaturização".

O novo chip escala essas paredes literalmente elevando-se acima delas. "Ao integrar memória e computação verticalmente, podemos mover muito mais informações muito mais rapidamente, assim como os elevadores em um prédio alto permitem que vários moradores se desloquem entre os andares ao mesmo tempo", disse Tathagata Srimani , professor assistente de engenharia elétrica e de computação na Universidade Carnegie Mellon, autor sênior do artigo, que iniciou o trabalho como pós-doutorando orientado por Mitra.

“A barreira da memória e a barreira da miniaturização formam uma combinação mortal”, disse Robert M. Radway , professor assistente de engenharia elétrica e de sistemas da Universidade da Pensilvânia e coautor do estudo. “Nós a atacamos de frente, integrando memória e lógica de forma precisa e, em seguida, construindo para cima com densidade extremamente alta. É como a Manhattan da computação – podemos acomodar mais pessoas em menos espaço.”

Como é fabricado o novo chip 3D

Até agora, a maioria das tentativas de criar chips 3D baseou-se no empilhamento de chips separados. Essa abordagem funciona, mas as conexões entre as camadas são grosseiras, esparsas e propensas a gargalos.

Em vez de fabricar chips separados e depois fundi-los, a equipe constrói cada camada diretamente sobre a anterior em um processo contínuo. Esse método "monolítico" utiliza temperaturas suficientemente baixas para evitar danos aos circuitos subjacentes, permitindo que os pesquisadores empilhem os componentes de forma mais compacta e os conectem com muito mais densidade.

Talvez ainda mais notável seja o fato de que todo o processo foi concluído em uma fundição de silício comercial nacional. "Transformar um conceito acadêmico de ponta em algo que uma fábrica comercial possa produzir é um desafio enorme", disse o coautor Mark Nelson , vice-presidente de operações de desenvolvimento tecnológico da SkyWater Technology . "Isso demonstra que essas arquiteturas avançadas não são apenas possíveis em laboratório – elas podem ser produzidas nacionalmente, em escala, que é o que os Estados Unidos precisam para se manter na vanguarda da inovação em semicondutores."

O desempenho e o potencial do chip

Os primeiros testes de hardware mostram que o protótipo já supera chips 2D comparáveis em cerca de quatro vezes. Simulações de versões futuras mais altas — com mais camadas empilhadas de memória e computação — apontam para ganhos ainda maiores. Projetos com camadas adicionais apresentam uma melhoria de até doze vezes em cargas de trabalho reais de IA, incluindo aquelas derivadas do modelo de código aberto LLaMA da Meta.

O mais impressionante é que, segundo os pesquisadores, o projeto abre um caminho realista para melhorias de 100 a 1.000 vezes no produto energia-atraso (EDP), uma métrica fundamental que equilibra velocidade e eficiência energética. Ao reduzir drasticamente o fluxo de dados e adicionar muito mais caminhos verticais, o chip consegue atingir tanto maior taxa de transferência quanto menor energia por operação, uma combinação que por muito tempo foi considerada inatingível para arquiteturas planas convencionais.

Os pesquisadores enfatizam que a importância a longo prazo desta pesquisa vai além do desempenho. Ao comprovar que chips 3D monolíticos podem ser construídos em solo americano, afirmam, o trabalho estabelece um modelo para uma nova era de inovação em hardware no país, na qual os Estados Unidos poderão projetar e fabricar os chips mais avançados.

Assim como a revolução dos circuitos integrados da década de 1980 foi impulsionada por estudantes que aprenderam a projetar e construir chips em laboratórios dos EUA, os pesquisadores afirmam que a transição para a integração 3D vertical e monolítica exigirá uma nova geração de engenheiros com domínio dessas tecnologias. Por meio de colaborações e fontes de financiamento como o Microelectronics Commons California-Pacific-Northwest AI Hardware Hub (Northwest-AI-Hub), estudantes e pesquisadores já estão sendo treinados para impulsionar a inovação em semicondutores nos Estados Unidos.

“Inovações como essa têm a ver, obviamente, com desempenho”, disse H.-S. Philip Wong , professor titular da Cátedra Willard R. e Inez Kerr Bell na Escola de Engenharia de Stanford e investigador principal do Northwest-AI-Hub. “Mas também têm a ver com capacidade. Se conseguirmos construir chips 3D avançados, podemos inovar mais rapidamente, responder mais rapidamente e moldar o futuro do hardware de IA.